Optimize Your z/OS Environment for Availability & Cost Efficiency

Workloads in the z/OS environment support business critical processes of major enterprises and must run smoothly at all times. At the same time, the z Systems costs for hardware and software should be as low as possible.

In this Tailored Services Engagement, IntelliMagic consultants will work with your site to optimize your CPU consumption and reduce MLC costs.

CPU Optimization Challenges

In this tailored services engagement, IntelliMagic will examine the current LPAR definitions, and based on collected SMF data, assess processor cache efficiency and recommend changes to LPAR weights and logical processor definitions as appropriate. After the customer has implemented the recommended changes, measurements of their impact on CPU efficiency will be presented.

CPU Optimization Analysis

Our consultants will leverage the visibility provided by IntelliMagic Vision into SMF data provided by the customer to identify potential opportunities to reduce CPU and associated software and hardware expenses.

Key Areas for CPU Optimization and MLC Reduction

After assessing your site, IntelliMagic experts will consult with you about your unique environment and cover all the potential areas where MLC savings are possible. Sites that have already optimized some aspects of their environments for MLC savings are often still able to identify additional savings.

IntelliMagic’s CPU Optimization service has led to significant MLC reductions, including some with 7-figure savings, for many mainframe sites.

Areas within scope of the analysis for the IntelliMagic consultant include:

- Initial hardware acquisition options (or evaluation of existing hardware)

- Configuring number and speed of individual cores to deliver required capacity

- Subcapacity and zIIP options

- For workloads under a TFP Software Consumption licensing model, evaluating CPU consumption and savings opportunities

- For workloads under a 4HRA licensing model, evaluating ways to minimize peak monthly 4HRA MSU values including timing and system placements of executing work, capping approaches.

- Optimizing processor cache efficiency (see below)

- LPAR configuration optimization, including:

- Number and configuration of LPARs

- LPAR weights and Hiperdispatch

- Reevaluating continued use of IRD for sites currently using it

Processor Cache Optimization

Processor cache efficiency is a largely overlooked area of CPU optimization that can provide significant reductions.

Some environments have achieved major CPU reductions through optimizing processor cache. In this service engagement, our consultants will explore configuration changes and approaches that could be used to reduce CPU.

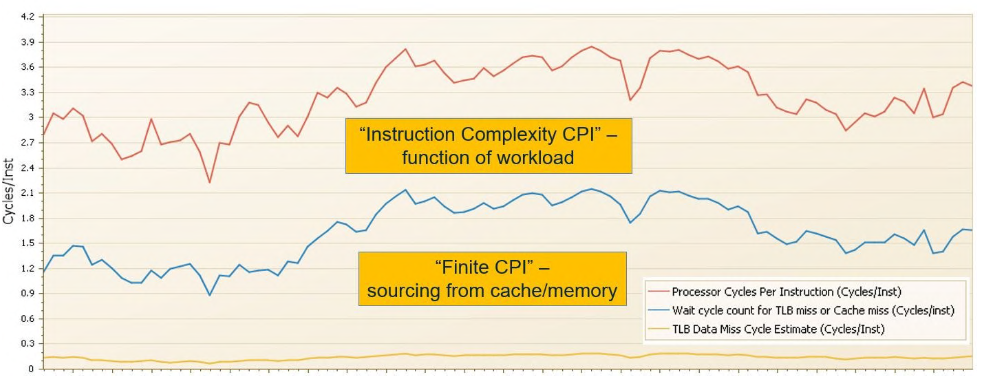

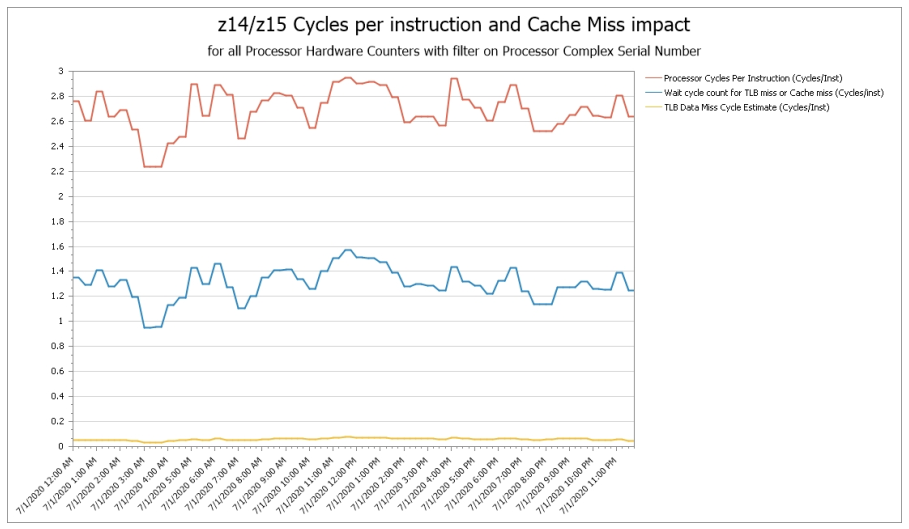

Distribution of Cycles per Instruction

Cycles Per Instruction can be divided into “Instruction Complexity CPI”, the area above the blue line that reflects “productive” cycles executing the instructions in a business workload, and “Finite CPI”, the area below the blue line that represents “unproductive” CPU cycles spent waiting for data and instructions to be staged from processor cache or memory into Level 1 cache.

These “waiting on cache” cycles represent a very significant portion of overall CPI and shows the magnitude of the potential opportunity for CPU and MLC reduction if improvements in processor cache efficiency can be achieved.

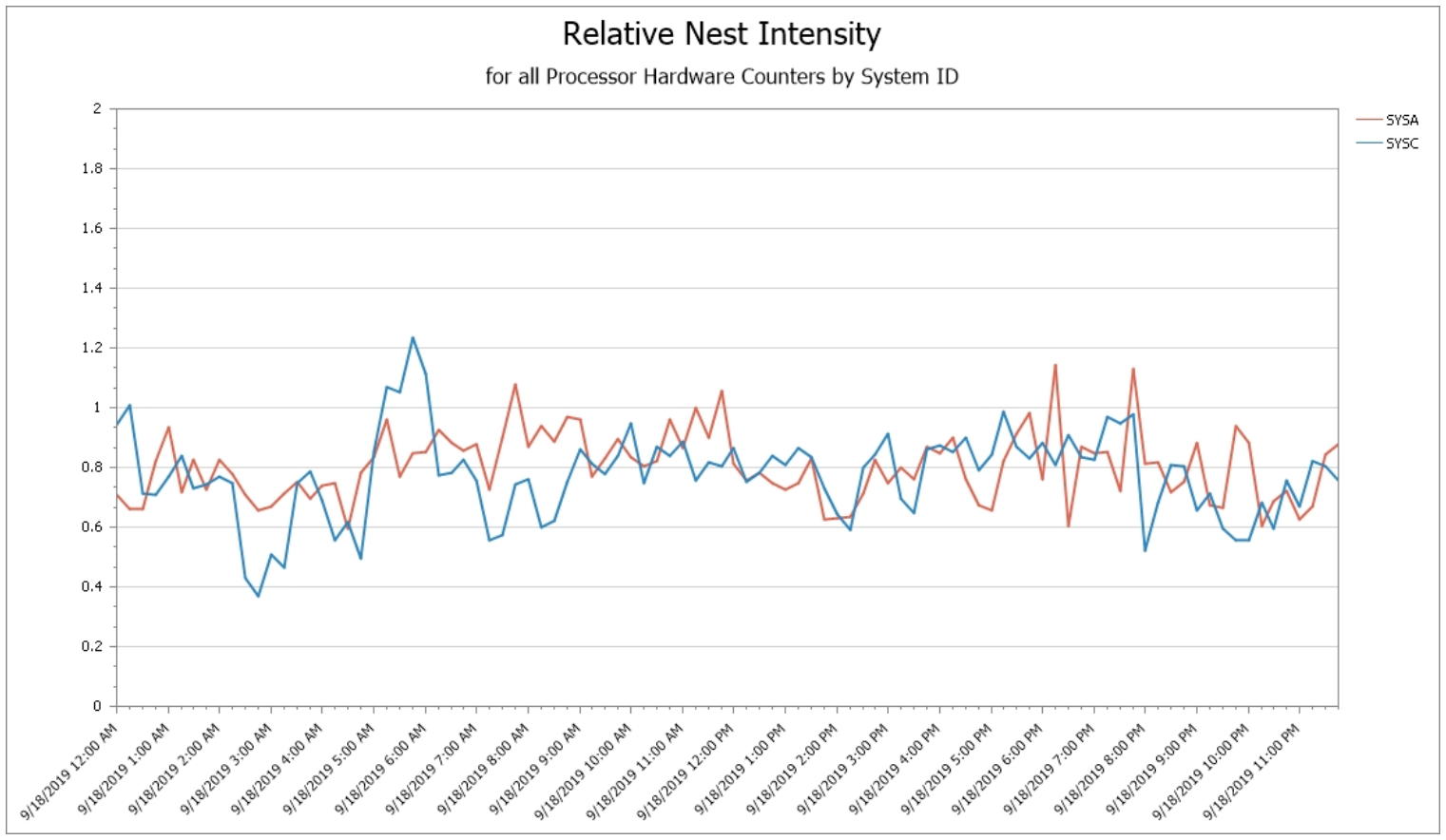

Relative Nest Intensity (RNI) by System

RNI quantifies how deep into the shared processor cache & memory hierarchy (called the nest) the processor needs to go to retrieve data and instructions when they are not present in Level 1 cache.

RNI is used (along with Level 1 Miss Percentage) to categorize a workload as High, Medium, or Low in the demand it places on the processor cache hierarchy. This workload classification is used to select the appropriate estimate of relative processor capacity from the IBM Large Systems Performance Reference (LSPR) chart.

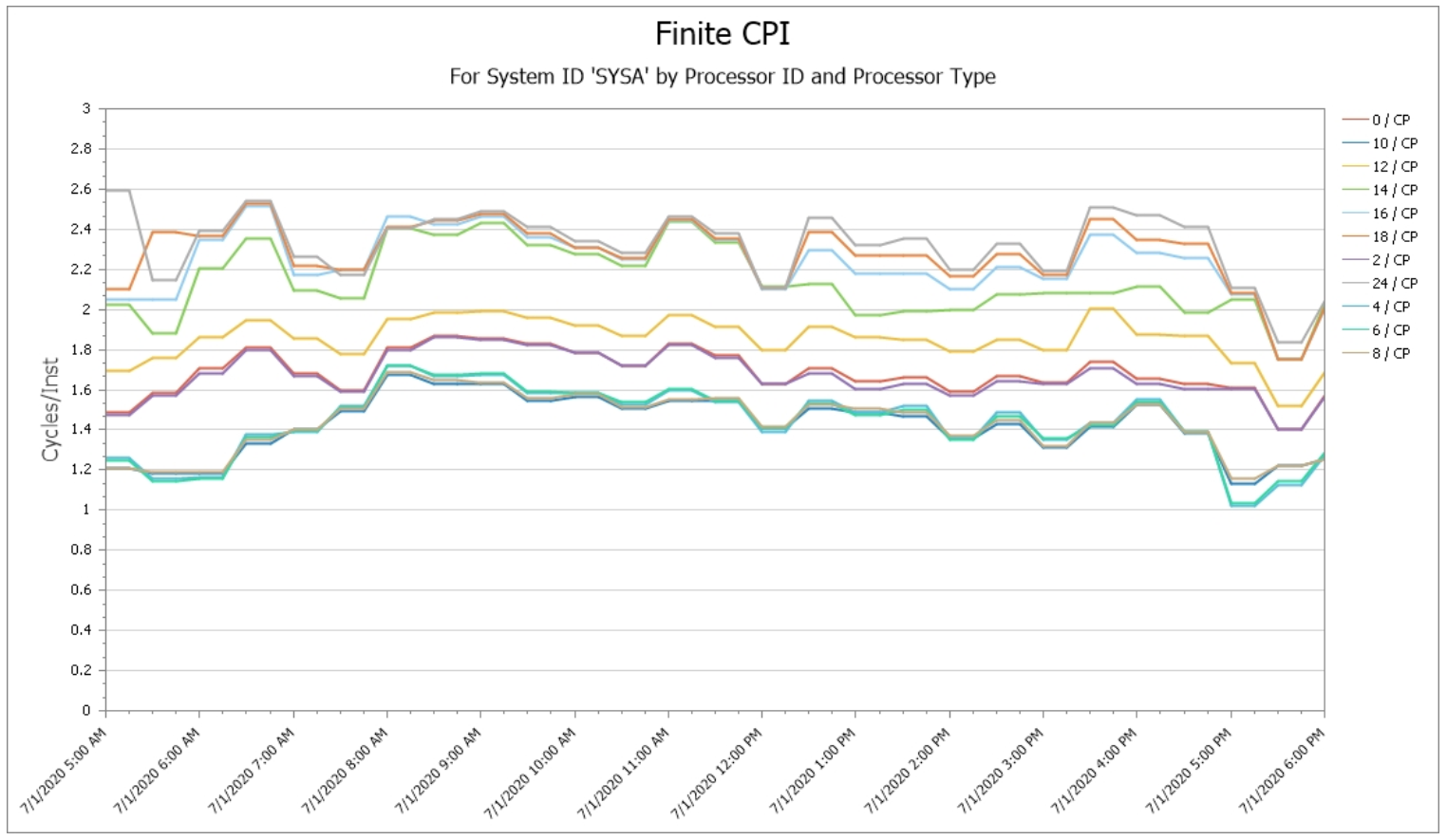

Finite CPI by Logical Processor

One characteristic of a workload that is important to be aware of is the increase in Finite CPI (“waiting cycles”) for the work not executing on Vertical High logical CPs. This “penalty” reflects the negative impact of contention for processor cache from workloads belonging to other LPARs. If there is a significant penalty, it is immediately apparent on this chart as reflected by a big gap in values separating the Vertical Highs from the Vertical Mediums and Lows.

Workload and Job-Level CPU Saving Opportunities

The IntelliMagic consultant will identify CPU reduction opportunities that may be applicable to your organization. Areas considered include:

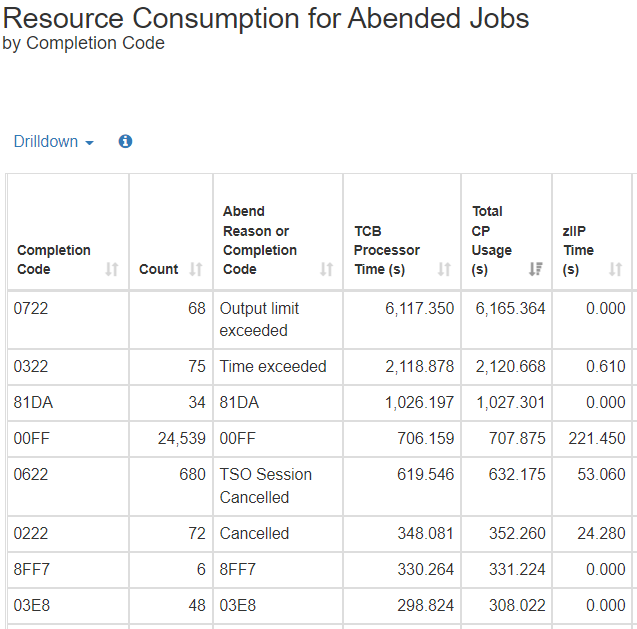

- Frequency and CPU impact of job abends, since every rerun consumes additional CPU in a SC solution.

- Proactively identify CPU surges by application. The IntelliMagic consultant will search for significant changes in the CPU consumption by address spaces and applications.

Request a Free CPU Optimization and Cost Reduction Consultation

Through IntelliMagic’s customized CPU Optimization and Cost Reduction Assessment and service, numerous z/OS sites of all sizes have identified areas for cost savings without compromising availability or performance, with some sites experiencing 7-figure savings.

At the start of the services engagement, our team will:

- Meet with the stakeholders to discuss the requirements of the CPU optimization study.

- Collect the required measurement data to build the IntelliMagic Vision database.

- Investigate the LPAR configuration.

- Investigate processor cache performance.

- Describes what needs to be changed (by LPAR) to enable efficient processor usage.

- Present a formal report describing the findings of the z/OS CPU optimization study.

- For sites under TFP, evaluate a wide range of potential CPU optimization opportunities to identify ones that may provide benefits for that customer.

Request a free consultation below with an IntelliMagic expert to answer your questions regarding this services engagement and gain an understanding of expected outcomes, timelines, process, and pricing. The engagement will be tailor fit to meet your specific environment and needs.